# LM20123 3A, 1.5MHz PowerWise<sup>®</sup> Synchronous Buck Regulator

#### **General Description**

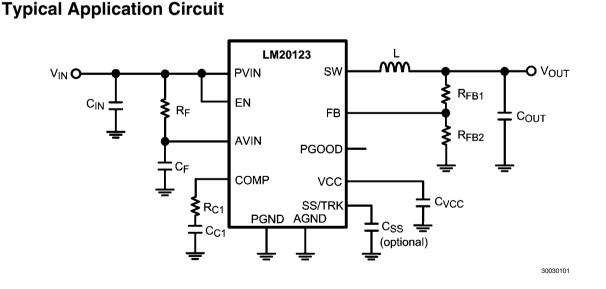

The LM20123 is a full featured 1.5 MHz synchronous buck regulator capable of delivering up to 3A of continuous output current. The current mode control loop can be compensated to be stable with virtually any type of output capacitor. For most cases, compensating the device only requires two external components, providing maximum flexibility and ease of use. The device is optimized to work over the input voltage range of 2.95V to 5.5V making it suited for a wide variety of low voltage systems.

The device features internal over voltage protection (OVP) and over current protection (OCP) circuits for increased system reliability. A precision enable pin and integrated UVLO allows the turn on of the device to be tightly controlled and sequenced. Start-up inrush currents are limited by both an internally fixed and externally adjustable Soft-Start circuit. Fault detection and supply sequencing is possible with the integrated power good circuit.

The LM20123 is designed to work well in multi-rail power supply architectures. The output voltage of the device can be configured to track a higher voltage rail using the SS/TRK pin. If the output of the LM20123 is pre-biased at startup it will not sink current to pull the output low until the internal soft-start ramp exceeds the voltage at the feedback pin.

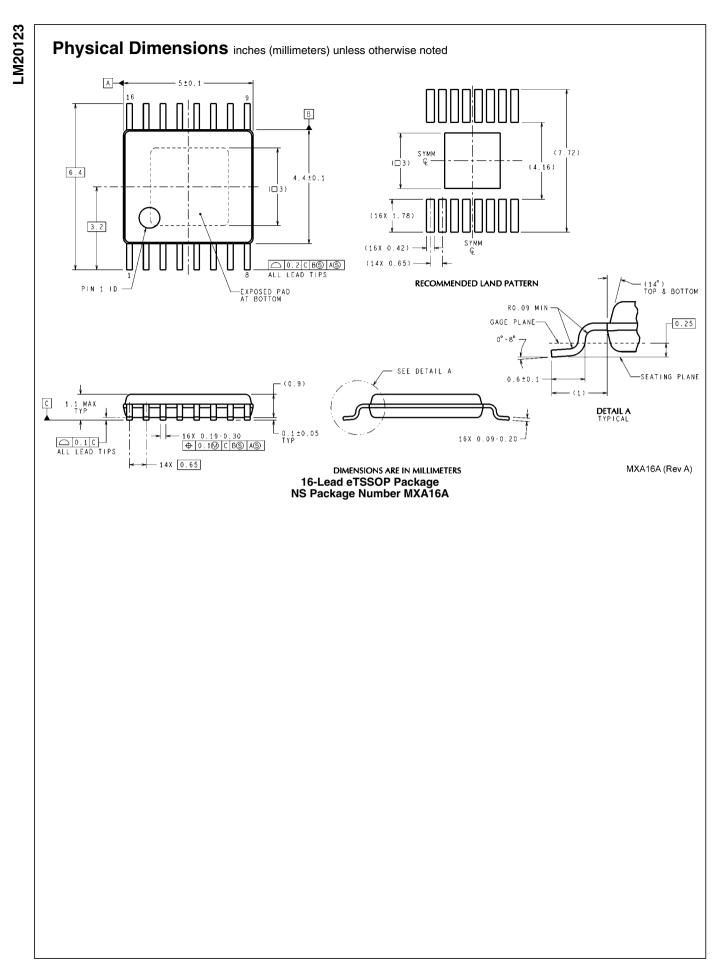

The LM20123 is offered in a 16-pin eTSSOP package with an exposed pad that can be soldered to the PCB, eliminating the need for bulky heatsinks.

#### Features

- Input voltage range 2.95V to 5.5V

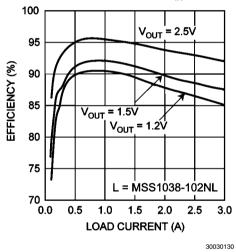

- Accurate current limit minimizes inductor size

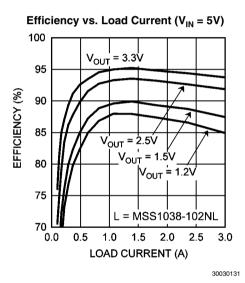

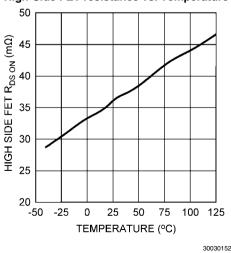

- 96% efficiency with 1.5 MHz switching frequency

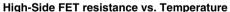

- 32 mΩ integrated FET switches

- Starts up into pre-biased loads

- Output voltage tracking

- Peak current mode control

- Adjustable output voltage down to 0.8V

- Adjustable Soft-Start with external capacitor

- Precision enable pin with hysteresis

- Integrated OVP, UVLO, power good and thermal shutdown

- eTSSOP-16 exposed pad package

#### Applications

- Simple to design, high efficiency point of load regulation from a 5V or 3.3V bus

- High Performance DSPs, FPGAs, ASICs and microprocessors

- Broadband, Networking and Optical Communications Infrastructure

PowerWise<sup>®</sup> is a registered trademark of National Semiconductor Corporation.

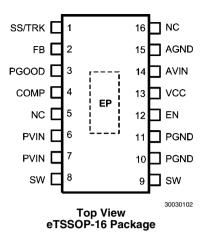

## **Connection Diagram**

# **Ordering Information**

| Order Number | Package Type | NSC Package Drawing | Package Marking | Supplied As                 |

|--------------|--------------|---------------------|-----------------|-----------------------------|

| LM20123MH    | eTSSOP-16    | MXA16A              | 20123MH         | 92 Units of Rail            |

| LM20123MHE   |              |                     |                 | 250 Units of Tape and Reel  |

| LM20123MHX   |              |                     |                 | 2500 Units of Tape and Reel |

# **Pin Descriptions**

| Pin # | Name        | Description                                                                                                                                                                                                                                                                                                                    |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SS/TRK      | Soft-Start or Tracking control input. An internal 5 $\mu$ A current source charges an external capacitor to set the Soft-Start ramp rate. If driven by a external source less than 800 mV, this pin overrides the internal reference that sets the output voltage. If left open, an internal 1ms Soft-Start ramp is activated. |

| 2     | FB          | Feedback input to the error amplifier from the regulated output. This pin is connected to the inverting input of the internal transconductance error amplifier. An 800 mV reference connected to the non-inverting input of the error amplifier sets the closed loop regulation voltage at the FB pin.                         |

| 3     | PGOOD       | Power good output signal. Open drain output indicating the output voltage is regulating within tolerance. A pull-up resistor of 10 k $\Omega$ to 100 k $\Omega$ is recommend for most applications.                                                                                                                            |

| 4     | COMP        | External compensation pin. Connect a resistor and capacitor to this pin to compensate the device.                                                                                                                                                                                                                              |

| 5,16  | NC          | These pins must be connected to GND to ensure proper operation.                                                                                                                                                                                                                                                                |

| 6,7   | PVIN        | Input voltage to the power switches inside the device. These pins should be connected together at the device. A low ESR capacitor should be placed near these pins to stabilize the input voltage.                                                                                                                             |

| 8,9   | SW          | Switch pin. The PWM output of the internal power switches.                                                                                                                                                                                                                                                                     |

| 10,11 | PGND        | Power ground pin for the internal power switches.                                                                                                                                                                                                                                                                              |

| 12    | EN          | Precision enable input for the device. An external voltage divider can be used to set the device turn-<br>on threshold. If not used the EN pin should be connected to PVIN.                                                                                                                                                    |

| 13    | VCC         | Internal 2.7V sub-regulator. This pin should be bypassed with a 1 $\mu$ F ceramic capacitor.                                                                                                                                                                                                                                   |

| 14    | AVIN        | Analog input supply that generates the internal bias. Must be connected to VIN through a low pass RC filter.                                                                                                                                                                                                                   |

| 15    | AGND        | Quiet analog ground for the internal bias circuitry.                                                                                                                                                                                                                                                                           |

| EP    | Exposed Pad | Exposed metal pad on the underside of the package with a weak electrical connection to ground. It is recommended to connect this pad to the PC board ground plane in order to improve heat dissipation.                                                                                                                        |

LM20123

### Absolute Maximum Ratings (Note 1)

Voltages from the indicated pins to GND

AVIN, PVIN, EN, PGOOD, SS/

TRK, COMP, FB, SW

Storage Temperature

Junction Temperature

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications. Power Dissipation (Note 2) Lead Temperature (Soldering, 10 sec) Minimum ESD Rating (Note 3) 2.6W 260°C LM20123

±2kV

### **Operating Ratings**

PVIN, AVIN to GND2.95V to 5.5VJunction Temperature-40°C to + 125°C

**Electrical Characteristics** Unless otherwise stated, the following conditions apply: AVIN = PVIN = VIN = 5V. Limits in standard type are for  $T_J = 25^{\circ}C$  only, limits in bold face type apply over the junction temperature  $(T_J)$  range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}C$ , and are provided for reference purposes only.

-0.3V to +6V

150°C

-65°C to 150°C

| Symbol                               | Parameter                                          | Conditions                         | Min   | Тур  | Max   | Unit |

|--------------------------------------|----------------------------------------------------|------------------------------------|-------|------|-------|------|

| V <sub>FB</sub>                      | Feedback pin voltage                               | V <sub>IN</sub> = 2.95V to 5.5V    | 0.788 | 0.8  | 0.812 | V    |

| ΔV <sub>OUT</sub> /ΔI <sub>OUT</sub> | Load Regulation                                    | I <sub>OUT</sub> = 100 mA to 3A    |       | 0.08 |       | %/A  |

| I <sub>CL</sub>                      | Switch Current Limit Threshold                     | V <sub>IN</sub> = 3.3V             | 4.3   | 4.8  | 5.3   | Α    |

| R <sub>DS_ON</sub>                   | High-Side Switch On Resistance                     | I <sub>SW</sub> = 3.5A             |       | 36   | 55    | mΩ   |

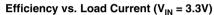

| R <sub>DS_ON</sub>                   | Low-Side Switch On Resistance                      | I <sub>SW</sub> = 3.5A             |       | 32   | 52    | mΩ   |

| l <sub>Q</sub>                       | Operating Quiescent Current                        | Non-switching, $V_{FB} = V_{COMP}$ |       | 3.5  | 6     | mA   |

| I <sub>SD</sub>                      | Shutdown Quiescent current                         | $V_{EN} = 0V$                      |       | 90   | 180   | μA   |

| V <sub>UVLO</sub>                    | VIN Under Voltage Lockout                          | Rising V <sub>IN</sub>             | 2.45  | 2.7  | 2.95  | V    |

| V <sub>UVLO_HYS</sub>                | VIN Under Voltage Lockout Hysteresis               | Falling V <sub>IN</sub>            |       | 45   | 100   | m∖   |

| V <sub>VCC</sub>                     | VCC Voltage                                        | I <sub>VCC</sub> = 0 μA            | 2.45  | 2.7  | 2.95  | V    |

| I <sub>SS</sub>                      | Soft-Start Pin Source Current                      | V <sub>SS/TRK</sub> = 0V           | 2     | 4.5  | 7     | μA   |

| V <sub>TRACK</sub>                   | SS/TRK Accuracy, V <sub>SS</sub> - V <sub>FB</sub> | $V_{SS/TRK} = 0.4V$                | -10   | 3    | 15    | m∖   |

| scillator                            | •                                                  | •                                  | •     |      |       |      |

| F <sub>osc</sub>                     | Oscillator Frequency                               |                                    | 1350  | 1500 | 1650  | kH   |

| DC <sub>MAX</sub>                    | Maximum Duty Cycle                                 | I <sub>LOAD</sub> = 0A             |       | 85   |       | %    |

| T <sub>ON_TIME</sub>                 | Minimum On Time                                    |                                    |       | 100  |       | ns   |

| T <sub>CL_BLANK</sub>                | Current Sense Blanking Time                        | After Rising V <sub>SW</sub>       |       | 80   |       | ns   |

|                                      | and Modulator                                      |                                    |       |      |       |      |

| I <sub>FB</sub>                      | Feedback pin bias current                          | V <sub>FB</sub> = 0.8V             |       | 1    | 100   | nA   |

| I <sub>COMP_SRC</sub>                | COMP Output Source Current                         | $V_{FB} = V_{COMP} = 0.6V$         | 80    | 100  |       | μA   |

| I <sub>COMP_SNK</sub>                | COMP Output Sink Current                           | $V_{FB} = 1.0V, V_{COMP} = 0.6V$   | 80    | 100  |       | μA   |

| 9 <sub>m</sub>                       | Error Amplifier Transconductance                   | $I_{COMP} = \pm 50 \ \mu A$        | 450   | 510  | 600   | μmł  |

| A <sub>VOL</sub>                     | Error Amplifier Voltage Gain                       |                                    |       | 2000 |       | V/\  |

| wer Good                             |                                                    |                                    |       |      |       |      |

| V <sub>OVP</sub>                     | Over Voltage Protection Rising Threshold           | With respect to V <sub>FB</sub>    | 105   | 108  | 111   | %    |

| V <sub>OVP_HYS</sub>                 | Over Voltage Protection Hysteresis                 |                                    |       | 2    | 3     | %    |

| V <sub>PGTH</sub>                    | PGOOD Rising Threshold                             | With respect to V <sub>FB</sub>    | 92    | 94   | 96    | %    |

| V <sub>PGHYS</sub>                   | PGOOD Falling Hysteresis                           | 7                                  |       | 2    | 3     | %    |

| T <sub>PGOOD</sub>                   | PGOOD deglitch time                                |                                    |       | 16   |       | μs   |

| I <sub>OL</sub>                      | PGOOD Low Sink Current                             | $V_{PGOOD} = 0.4V$                 | 0.6   | 1    |       | mA   |

| I <sub>OH</sub>                      | PGOOD High Leakage Current                         | $V_{PGOOD} = 5V$                   | 1     | 5    | 100   | nA   |

LM20123

| Symbol              | Parameter                   | Conditions             | Min  | Тур  | Max  | Unit |

|---------------------|-----------------------------|------------------------|------|------|------|------|

| _ogic               |                             |                        |      |      |      |      |

| $V_{IH\_EN}$        | EN Pin Turn on Threshold    | V <sub>EN</sub> Rising | 1.08 | 1.18 | 1.28 | V    |

| V <sub>EN_HYS</sub> | EN Pin Hysteresis           |                        |      | 66   |      | mV   |

| hermal Shutd        | own                         |                        | •    |      |      |      |

| T <sub>SD</sub>     | Thermal Shutdown            |                        |      | 160  |      | °C   |

| T <sub>SD_HYS</sub> | Thermal Shutdown Hysteresis |                        |      | 10   |      | °C   |

| hermal Resist       | tance                       |                        | •    |      |      |      |

| $\theta_{JA}$       | Junction to Ambient         |                        |      | 38   |      | °C/W |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. **Note 2:** The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J_{\_}MAX}$ , the junctions-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_{A}$ . The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_{D_{\_}MAX} = (T_{J_{\_}MAX} - T_{A})/\theta_{JA}$ . The maximum power dissipations of 2.6W is determined using  $T_{A} = 25^{\circ}$ C,  $\theta_{JA} = 38^{\circ}$ C/W, and  $T_{J_{\_}MAX} = 125^{\circ}$ C.

Note 3: The human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor to each pin.

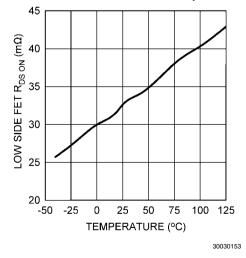

**Typical Performance Characteristics** Unless otherwise specified:  $C_{IN} = C_{OUT} = 100 \ \mu\text{F}$ , L = 1.0  $\mu\text{H}$  (Coilcraft MSS1038),  $V_{IN} = 5V$ ,  $V_{OUT} = 1.2V$ ,  $R_{LOAD} = 1.2\Omega$ ,  $T_A = 25^{\circ}\text{C}$  for efficiency curves, loop gain plots and waveforms, and  $T_I = 25^{\circ}\text{C}$  for all others.

Low-Side FET resistance vs. Temperature